スニペットは、テキスト文字列から構成された情報群を意味します。例えば、サンプル・コードの断片がスニペットに相当します。

スニペット機能は名称に対してコードの断片をマップしますが、ブックマーク機能は名称に対してソース・ファイルの行をマップします。

コード・スニペット機能、及び、ブックマーク機能の組み合わせを利用する事により、コード開発時の生産性を向上する事が出来ます。

詳細は、こちらを参照して下さい。

スニペットは、テキスト文字列から構成された情報群を意味します。例えば、サンプル・コードの断片がスニペットに相当します。

スニペット機能は名称に対してコードの断片をマップしますが、ブックマーク機能は名称に対してソース・ファイルの行をマップします。

コード・スニペット機能、及び、ブックマーク機能の組み合わせを利用する事により、コード開発時の生産性を向上する事が出来ます。

詳細は、こちらを参照して下さい。

既に検証機能を保有しているユーザ向けに、lightweight SystemVerilg IDE を開発しました。

詳細は、こちらを参照して下さい。

2018年11月14日(水)〜16日(金)パシフィコ横浜にて開催の「ET & IoT Technology 2018」に出展致します。

出展案内

SystemVerilog IDEを展示しますので、ご来場の際には弊社ブースにもお立ち寄り下さい。

講演案内

展示会場内 セミナー会場B にて講演を行います。

日 時 :2018年11月16日(金) 11:30-11:55

会 場 :展示会場内 セミナー会場B EDA-1

タイトル:UVMの概要と実践に適用する際のガイドライン(UVMの理解と検証作業への応用)

事前登録画面にて EDA-1 電子設計・EDAトラック をチェックして下さい。

同トラック内の他のセッションもご聴講下さい。

ダウンロード・ページにお進み下さい。

2018年11月14日(水)〜16日(金)パシフィコ横浜にて開催の「ET & IoT Technology 2018」に出展致しました。

弊社ブースにお立ち寄り頂いた方、及び、UVMに関する講演をご聴講して頂いた方々に御礼申し上げます。

講演で使用した資料はダウンロード・ページから入手する事が出来ます。資料には、講演では省略した内容も含まれています。

このチュートリアルを通して、SystemVerilogによる検証の基礎からUVMを適用するまでに必要な知識を習得する事が出来ます。

名 称 :JEVeC DAY 2018

会 場 :川崎市産業振興会館

日 時 :2018年12月11日(火) 14:30-15:30

タイトル:SystemVerilog from Zero to One(検証の基礎からUVM適用までの実践知識を習得)

無料で参加する事が出来ます。詳細は、日本EDAベンチャー連絡会(JEVeC)のホームページを参照下さい。

入力ナビゲータ、及び、SystemVerilogテキスト・エディタの機能が強化されました。

ここでは簡単な例を紹介します。更なる詳細は、ダウンロード・ページから資料を取得して下さい。

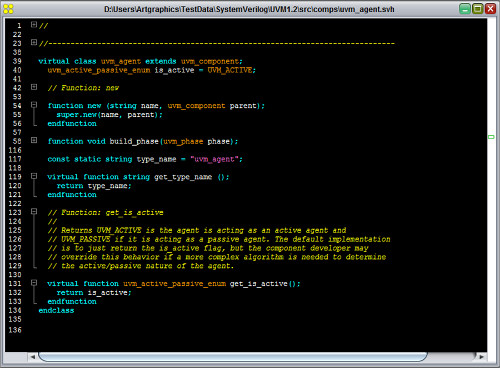

行の折り畳み機能は非常に便利です。特に、クラス内に複雑なタスク、及び、ファンクションが定義されている場合、注目したい箇所を中心に表示する事が出来ます。例えば、左図は、uvm_agentクラスを表示しています。1ページに全容が表示されています。

行の折り畳み機能は非常に便利です。特に、クラス内に複雑なタスク、及び、ファンクションが定義されている場合、注目したい箇所を中心に表示する事が出来ます。例えば、左図は、uvm_agentクラスを表示しています。1ページに全容が表示されています。

大きなファイルで作業する場合、ファイル内の異なる行に移動する事が頻繁に発生します。特に、直前に編集した行に戻る為には何度もウィンドウをスクロールする操作をしなければなりません。

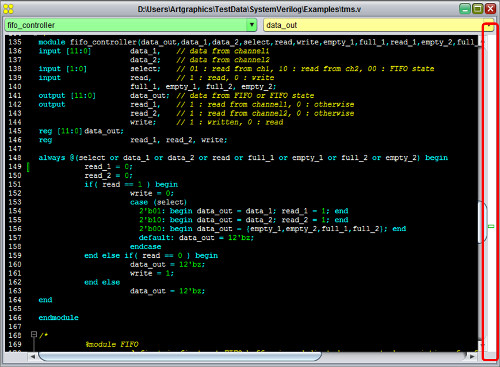

大きなファイルで作業する場合、ファイル内の異なる行に移動する事が頻繁に発生します。特に、直前に編集した行に戻る為には何度もウィンドウをスクロールする操作をしなければなりません。SystemVerilog IDEのFPSは直前に編集した行を小さな矩形として表現します。その矩形をクリックすると編集行に戻る事が出来ます。

左図に於ける赤い矩形に囲まれた白い領域がFPSナビゲータです。ナビゲータ内の小さな矩形は直前に編集した行を表現しています。その矩形をクリックすると149行が見える様にテキスト・ウィンドウがスクロールします。同様に、直前に選択した文字列に関してもナビゲータが表示されます。

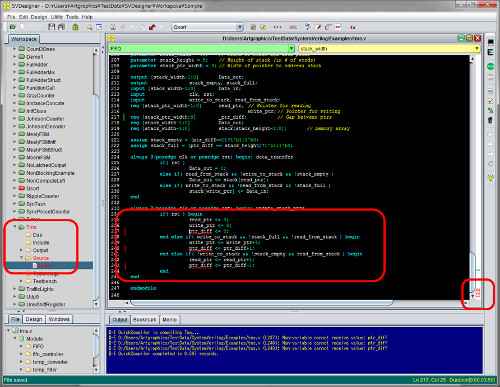

コンパイル・エラーが存在する場合、テキスト・エディタ内のエラー箇所を簡単にナビゲーションする機能を備えています。左図は、コンパイル・エラーが存在する例を示しています。エラーが存在する事を容易に認識する事が出来ます。

SystemVerilog IDEはファイルのバックアップを自動的に作成します。バックアップからファイルを復元する事、バックアップ・ファイルを参照する事、ファイルとバックアップとの比較をする事等の操作はマウスクリックだけで簡単に済みます。各ファイルに対して最大100個のバージョンを保持する事が出来ます。自動バックアップ機能は簡易型VCS(Version Control System)として作業環境の保全性を高めます。

詳細は、こちらを参照して下さい。

HTML文書生成機能が改訂され使い易くなりました。そして、この機能がSystemVerilog IDEの標準機能となりました。

設計・検証作業の報告、レビュー、確認、使用法の説明等多くの利用法が考えられます。

詳細は、こちらを参照して下さい。

デザイン・スタイル・チェック(DSC)は、SystemVerilog記述が、企業、プロジェクト、及び、契約等で定めた規格、ルール、標準等に遵守しているかを確認する機能です。

DSCの機能が拡張されUVM検証コードをQualifyする様になりました。この機能は、UVMを使用する際に必要なルールを満たしている事を確認します。検証コード作成時に潜在的問題を未然に防ぐ事で生産性が向上します。詳細は、こちらを参照して下さい。

微力ながらSystemVerilogの有用性を普及する事が出来たと思うので、この決定に至りました。

好ましくないダウンロードが後を絶たない為、終止符を打ちました。

この終了がSystemVerilogの習得を目的にしている方々を失望させる事は非常に残念だと思います。

ご理解下さる様お願い申し上げます。

SystemVerilogに関する最新の資料はこちらも参照下さい。

SystemVerilog IDE、及び、SystemVerilog Checker のレイアウト制御が強化されました。

この機能により、プロジェクト・エクスプローラ、コンソール、テキスト・エディタ画面の管理を簡潔な操作で行えます。

「SystemVerilog入門」及び「UVM入門」を大幅に書き直し、利用し易い参考書形式に改訂しました。

詳細は、こちらを参照下さい。

検証作業に欠かせないSystemVerilogに関する知識を包括的に書物としてまとめました。

詳細は、こちらを参照して下さい。

既存の多くの書物は、シンタックスをベースにして機能を淡々と紹介するだけに過ぎない為、SystemVerilogの知識を習得する目的には適合しません。本資料は、SystemVerilogの備える機能の本質を解説します。物事の本質を理解すれば、標準的な応用だけでなく、非標準的な応用にも臨機応変に対応する事が出来る能力を養う事が出来ます。本資料は、検証機能を除くSystemVerilog全般の基礎知識、及びその応用としてRTLデザインの記述法を主題に解説しています。SystemVerilogへの初心者及び設計技術者にお薦めします。

詳細は、こちらにお進み下さい。

「実践SystemVerilog入門」は、「SystemVerilogによる設計と検証」に改訂されました。

内容的には、下記の書籍内容に匹敵します。

SystemVerilog入門、共立出版

SystemVerilogによる検証の基礎、森北出版

実践UVM入門、森北出版

詳細は、技術資料のページをご覧ください。

SystemVerilogによるモデリングを典型的な回路を例にとり記述した資料です。

詳細は、こちらを参照下さい。

SystemVerilogの重要性にも関わらず、未だに本格的な入門書が国内で出版されていません。

SystemVerilogを正しく、かつ的確に使用するためには、確実な基礎知識が必要です。

単なるシンタックスベースの解説では、一面的な解説に終わり応用力を養う事はできません。

弊社の技術資料は、LRMを忠実に解説した厳密な資料です。言語では、多種多様な記述法が可能であるため、

SystemVerilogの原理原則を正しく理解する事から学習を始める必要があります。

詳細は、こちらでお進み下さい。

弊社技術資料「SystemVerilog入門」の書籍化が決定しました。

詳しくは、こちらを参照して下さい。

SystemVerilog IDE は、Windowsの環境で快適に動作するSystemVerilog設計・検証ツールです。

テレワーク環境でも、自身のPCでSystemVerilogに関する作業を円滑に遂行する事が出来ます。

「実践SystemVerilog入門」を大改訂し、「SystemVerilogによる設計と検証」と改めました。

これに伴い、「実践SystemVerilog入門」の提供を終了します。

本資料は、UVMに関する知識を習得する支援をするために準備されました。具体的には、EVEと呼ばれる小規模なSystemVerilog検証パッケージを例にとり、検証環境構築技術を詳説しています。SystemVerilogクラスを使用する技術、マクロの使い方、UVMのコア機能に関する知識を完全に習得する事が出来ます。

共立出版社より、「SystemVerilog入門」は10月上旬に刊行されます。現在、ネット予約受付中です。

本書は、SystemVerilogの基礎知識を厳密かつ正確に解説した国内初の言語解説書です。

SystemVerilogを的確に使用するために、本書はハードウェア技術者にとって必読の書です。

「実践UVM入門」として森北出版から発売されています。

詳細は、こちら。

本書は、これからSystemVerilogを学ぼうとしている設計者向けに書かれた資料です。

設計分野で使用されるSystemVerilogの機能を中心に解説を進め、ハードウェアを実装する為の基礎知識を提供します。

詳細は、こちら。

ソースコードをプロジェクトに登録し、ビルドボタンをクリックするだけで実行イメージが作成されます。

何回でも実行イメージを起動する事ができるので、一回のコンパイルで複数回の検証作業を済ませる事ができます。

シミュレータは、制約付きランダムスティミュラス生成、ファンクショナルカバレッジ、アサーション、UVM、DPIをサポートしています。

アサーション、及びファンクショナルカバレッジの実行結果を確認するためのGUIも別アプリとして標準的に備わっています。

「 SystemVerilog による検証の基礎(森北出版)」に掲載されている使用例のソースコードが公開されました。

ダウンロードはこちら。

「 SystemVerilog 入門(共立出版)」に掲載されている使用例のソースコードが公開されました。

ダウンロードはこちら。

「実践UVM入門」のネット予約が開始しました。

詳細は、技術資料のページをご覧ください。

「実践UVM入門」のネット予約が可能になりました。

詳細は、技術資料のページをご覧ください。

「どんな本を読んでもSystemVerilogを良く理解できない」という方にお薦めする資料です。

本資料は、SystemVerilogの基礎的な知識をハードウェアを記述する観点から「超」詳しく解説しています。

基礎知識の解説に限らず、クラス、インターフェース、パッケージ等の高度な概念の解説も含まれているので、

SystemVerilog初心者だけでなく中級者レベルを目指す実務者にも最適な資料です。

資料のサンプルはこちら。

SystemVerilogの仕様は数年に一度改訂され、最新仕様はIEEE Std 1800-2017として2018年2月21日に公開されました。

この仕様書には、多くの機能追加と過去の機能の整理整頓が含まれています。例えば、オペレータオーバーローディング

は、もはや、最新仕様に含まれていません。

古い仕様を基にした参考書で学習しても、最新仕様で再度学習し直さなければ実務でSystemVerilogを駆使する事はできません。

実務者には「SystemVerilog入門」をお薦めします。

スケジューリングの仕組み、プロセスの実行順序、タイミング制御等の基本的知識を会得したい技術者向けの資料です。

詳細は、こちら。

「SystemVerilog雑談」は、SystemVerilogに関する役立つ情報を紹介します。

一つ一つの話題は簡潔にまとめられているので、読み易くなっています。

興味のある方は、ダウンロードページにお進み下さい。

この書物は、SystemVerilogユーザを対象に書かれたプログラミング技術書で、SystemVerilogが備える

機能を正確、かつ的確に使用するための解説を多く含みます。詳しくは、 こちら を参照して下さい。

補足説明が追加されて、更に読み易くなりました。SystemVerilogを確実に理解したい方に薦めます。

詳細は、こちらへ。

Windows 10 から Windows 11へアップグレードされたユーザの方も多いかと思います。

SystemVerilog IDE は、Windows 11においても従来通り使用できます。

周知のように、PCに搭載されているCPUの性能は日進月歩で向上されています。

この様な時代においては、Linuxサーバーだけに頼らずに、常時携帯しているPCを

最大限に活用した業務遂行形態を推奨するのは自然な成り行きです。

特に、リモートで作業をしなければならない状況が多い技術者にとっては、

お手元のPC上でハードウェアの設計・検証作業を遂行できるEDAツールは

時代が求める存在です。詳細は、こちらへ。

更に詳しい機能解説・注意事項を追加しました。

サンプルはこちらへ。

森北出版より、「検証のためのSystemVerilogプログラミング」が発売になります。

現在、ネット予約受付中です。詳細は、こちら。

森北出版より、「検証のためのSystemVerilogプログラミング」が発売されました。

店頭で立ち読みして決定する価値のある書物です。本書の意義は、内容を見なければ分かりません。

特に、SystemVerilogの入門書を読んだ後に、学習した内容を確認するための資料として最適です。

SystemVerilogで論理回路を表現する技術を詳しく解説した他に類を見ない技術資料です。

この書を読めば、マルチプレクサを活用して様々な論理回路を表現する知識・技術を習得できます。

整数演算の基礎技術、組み合わせ回路とシーケンシャル回路のモデリング手法の解説も含まれています。

詳細は、こちらへ。

ファンクショナルカバレッジとアサーションを分かり易く解説した資料を追加しました。

詳細は、こちらへ。

例えば、以下のような操作でコードの開発を進める事ができます。コード入力中に大半のシンタックスチェックが終了するのでコード開発はスムーズに進行します。

① CTRL+Wでセッションを開始します。

② CTRL+Pでプロジェクトを作ります。

③ 簡単なマウスクリック操作で空ファイルをプロジェクトに登録します。

④ CTRL+SHIFT+Mでモジュールのスケルトンを作ります。

⑤ ショートカットキーを併用してコードの入力を進めます。

⑥ クラスの作成にはウィザードを使用できます。

⑦ 入力したソースコードをCTRL+Sで保存するとシンタックスチェックが行われます。

⑧ エラーがあれば明示されます。

⑨ 頻繁に参照するコードにはブックマークを付けて簡単にアクセスできるようにします。

⑩ 既存のコードサンプルを参照するにはスニペット機能を使えます。

⑪ コードの準備ができたらCompileボタンをクリックすると、実行モジュールができます。

⑫ Runボタンをクリックするとシミュレーションが開始します。

参考

CTRL+WとはCTRLキーを押しながらWキーを押す操作です。他のキーの組み合わせも同様です。

SystemVerilog IDE には、コード開発を支援するための機能が多く備わっています。

その殆どの機能は自動的に開始するので、ユーザが特別な準備をする必要がありません。

例えば、ファイルのバックアップ機能は自動的に作動するので、万一、編集中にソースコードが破損しても

編集作業を開始した時点に容易に戻れます。また、コード開発中には各種のナビゲータが自動的に作動し、

キー入力の負荷軽減を促進します。例えば、alwと入力すると、一致する可能性のあるSystemVerilogキーワード

の一覧が表示されるので、意図するキーワードを選択してENTERキーを押すと入力が完結します。

このような入力支援機能は作業の効率化を促進するだけでなく、タイプミスの軽減にも貢献します。

しかも、CTRL+Sでファイルを保存するとシンタックスチェックが自動的に行われます。

更に詳しい解説は、ダウンロードページから「SystemVerilog 設計検証ツール製品紹介」を取得して下さい。

本書は、初心者向けに詳しく書かれたSystemVerilogの入門書です。

特に、これからSystemVerilogを学ぼうとしている方に最適です。

ネット予約開始までもうしばらくお待ちください。

サンプルは、こちらへ。

共立出版より販売されている「SystemVerilog入門」の重版が決定しました。

現在、入手が困難な状態が続いていると思いますが、もう暫くお待ちください。

共立出版より、「SystemVerilog超入門」が2023年7月10日に発売されます。

現在、ネット予約受付中です。詳細は、こちらへ。

共立出版より、「SystemVerilog超入門」が2023年7月10日に発売されます。

書籍概要および目次が出版社のウェブサイトに公開されました。

現在、ネット予約受付中です。詳細は、 こちら へ。

2023年7月10日に、共立出版から「SystemVerilog超入門」が発売になりました。

店頭で立ち読みして、購読を決定すると良いです。

ご自身にあう入門書であるかどうかを判断すると良いです。

SystemVerilog IDEを紹介する短いビデオができました。

製品評価をする判断基準としてデモビデオをご利用ください。

SystemVerilog IDEが使い易いGUIで構成されている事は一目瞭然です。

ご興味のある方は、こちらへ。

共立出版より、「SystemVerilog超入門」の練習問題が公開されました。

練習問題には詳しい解答が付いているので、学習内容の確認をできます。

書籍紹介ページに行き「関連情報」のタブをクリックすると練習問題を取得できます。

SystemVerilog IDE がポピュラーな Ubuntu ディストリビューションの環境で使用できるようになりました。

SystemVerilog IDE は SystemVerilog ソースコードを自動管理するので、コンパイルからシミュレーションまでの作業は

マウスクリックだけで完了します。SystemVerilog IDE には開発機能だけでなく、SystemVerilog の検証機能及び

検証結果を確認するための検証ビューワーも標準的に備えられています。

SystemVerilog IDE に備えられているテキストエディタは使い易く、ユーザの生産性向上を促進します。

マイクロソフト社が提供する WSL 機能を SystemVerilog IDE に組み込みました。

これにより、WSLでインストールしたLinuxディストリビューションを SystemVrilg IDE と共に使用できます。

特に、SystemVerilog シミュレーションに Linux ディストリビューションが使用されます。

詳細は、こちらへ。

SCL は TLM (Transaction Level Modeling) ベースの検証環境構築用の SystemVerilog クラスライブラリーです。

SCL には検証環境を構築するために必要なベースクラス、トランザクションを定義するベースクラス、トランザクション

を生成する手順のベースクラス等便利な機能が備わっています。

SCL では、トランザクション生成過程をツリーで表現するので分かり易く SystemVerilog 初心者でも短期間に習得できます。

しかも、軽量な SystemVerilog クラスライブラリーとして実現されているので、コンパイル時間も早く生成される

実行モジュールも小さいという利点があります。

SystemVerilogで検証環境を構築する計画を検討されている法人様には SCL をおすすめします。

旧版「SystemVerilogによるロジック設計入門」を改訂し、SystemVerilogによる設計とモデリングの基礎

を懇切丁寧に解説する資料を作りました。解説は、基本回路をSystemVerilogで記述する知識と技術を習得する

過程から始まり、組み合わせ回路、シーケンシャル回路、FSMの設計技術へと発展して行きます。

本書は、SystemVerilog記述を論理回路に合成する知識と技術を養えるユニークな技術資料です。

この資料は、わかり易く書かれたSystemVerilog Class Library (SCL) の仕様書です。

SCLは、UVMと異なり理解し易いアーキテクチャを採用しているので学習時間が多くかかりません。

しかも、SCLは拡張し易い構造になっているので、ユーザ自身によるカスタマイズが可能なパッケージです。

UVMに代わる検証パッケージをお探しの方は、是非ご覧下さい。

検証環境ではパターンを指定して名称の検索が行われますが、SystemVerilogには対応する機能が

備わっていないため、DPI-C に依存するのが一般的です。しかし、その方法は不便であるだけでなく、

ポータビリティにも乏しいので望ましい検証手段とは言えません。

SCL の新しいバージョンではパターンマッチング機能を使用できるようになりました。

例えば、パターン test*.generator を指定して generator と呼ばれるインスタンスにシナリオを割り当てます。

その他、パターンを指定してコンフィギュレーションの変更をする際、DPI-C に依存しなくて済みます。

検証環境のコンフィギュレーションを一時的に変更したい場合があります。

新しいバージョンのドライバーを検証環境に変更を加えずにテストしたい場合等が一例になります。

例えば、以下のように指定すると driver_t クラスは、一斉に new_driver_t クラスに変化します。

`scl_change_type_m(driver_t,new_driver_t)

クラスタイプの変更に限らず、クラス内に定義されているプロパーティの設定を一時的に変更する事もできます。

この便利な機能を使用する事により、検証環境開発作業の生産性は著しく向上します。

SystemVerilog でのプリント処理で悩ましいのがカラムを揃える事と2進や16進の表現形式です。

また、カラムヘッダの名称変更やビット幅の変更でさえコードの書き換えを余儀なくさせます。

これらの問題を解消するために、自動カラム調節を行うプリント機能を開発しました。

プリント用のレイアウトをヘッダと呼ばれるデータ構造で定義すると、カラムに表示する値を設定するだけで、

カラム位置の自動調節が行われます。そして、表現形式の変更は使用するマクロ名を変更するだけで済みます。

例えば、以下のようにヘッダを定義して、ヘッダと共にプリントするとカラム位置が自動的に調節されます。

scl_print_header_s header[] = '{

'{"time",5,SCL_HEADER_DEFAULT},

'{"clk",3,SCL_HEADER_DEFAULT},

'{"reset",5,SCL_HEADER_DEFAULT},

'{"d",`scl_full_hex_digits_m(WIDTH),SCL_HEADER_DEFAULT},

'{"q",`scl_full_hex_digits_m(WIDTH),SCL_HEADER_DEFAULT}

};

仮に、ビット幅(WIDTH)を変更しても自動的にカラム位置が調節されます。

この便利な機能を使用する事により検証結果のプリント処理は著しく省力化されます。

スコアボードに predict() メソッドを追加し、DUTからの出力を検証する仕組みを整えました。

スコアボードは、DUTをドライブするために使用された入力を基にして predict() メソッドにより結果を予測し、

DUTからの出力が予測された値と一致するかの判定をする役目を持ちます。今回の機能拡張により、

スコアボードで実行結果の検証、モニターでは簡単なカバレッジ計算を行うという作業分担が確立しました。

これらの機能を SCL の汎用的な検証結果レポート機能と併せて使用すると、検証作業の生産性は著しく向上します。

ノンブロッキング方式でトランザクションの授受を行える TLM ポートを追加しました。

また、トランザクションをプーリングする機能を持つ FIFO クラスも追加しました。

FIFO はブロッキング方式でもノンブロッキング方式でも使用できます。

SystemVerilogのプロセスの実行開始順序は不定であるため、シミュレーション結果は実行環境に依存します。

ランダム性を回避するためには、SystemVerilogのシミュレーション論理を理解しなければなりません。

本資料は、SystemVerilogのスケジューリングの仕組み、プロセスの実行順序、タイミング制御等の

基本的知識を会得したい技術者向けの豆辞典です。

詳細は、こちらへ。

SystemVerilogの改訂版が,2024年2月28日に IEEE Std 1800-2023 として公開されました。

LRM の一読をすすめます。

周知のように SystemVerilog が改訂され IEEE Std 1800-2023として公開されました。

この改訂版は設計分野で使用される機能の追加を含みませんが、検証分野で有益な機能を多く含んでいます。

追加された機能は、検証システムの開発作業の品質を高める効果と検証システムの保守を容易にする効果があります。

したがって、現在および将来の検証システム開発に取り入れるべき機能が多く見当たります。

SystemVerilog IDE は、これらの新機能を標準的にサポートしています。

例えば、ベースクラスに定義されているvirtualメソッドをサブクラスで拡張するとします。

もし、サブクラスのメソッドの引数リストがベースクラスのメソッドの引数リストと一致しなければ、

virtualメソッドの拡張にはならず、サブクラス独自のメソッドを定義した事になります。

当然、コンパイルエラーは出ませんが、サブクラスのメソッドの動作は正しくありません。

このような致命的な誤りを未然に防ぐために、:extends 機能が追加されました。

この機能を使用する事により、自明な誤りから解放されると共に検証システムの品質が向上します。

2024年8月29日に開かれるDVCon Japan 2024に於いて、 IEEE Std 1800-2023のチュートリアルをします。

周知の方も多いと思いますが、SystemVerilogの改訂版が2024年2月28日に公開されました。

本チュートリアルでは、改訂版に追加された新機能を中心に解説します。

ご興味のある方は、是非、参加して下さい。

主題:IEEE Std 1800-2023の要約 (A Subjective Review on IEEE Std 1800-2023)

講師:篠塚一也

SystemVerilogは、設計分野および検証分野で使用されるハードウェア記述言語ですが、

何れの分野で使用されるにしても、間違いのない正しい記述をしなければなりません。

本書では、SystemVerilogの基礎知識だけでなく、技術者自身の創造力、独創性、そして

“ひらめき”が適切な成果と新発見に結びつく例を紹介します。

また、各章の終わりには練習問題が追加されました。詳しい解答もついています。

SystemVerilog IDE 製品紹介を更新しましたので、ご覧下さい。

IDE が備える機能を分かり易く紹介したプレゼンテーション資料です。

論理合成システムはRTL記述によるデザインの性能をいち早く予測するための機能です。

論理合成システムは、ユーザ指定のライブラリーを使用してRTL記述からネットリストを生成します。

ユーザは、生成されたネットリストを基にして様々な解析ツールによりデザインの性能を測定する事ができます。

論理合成システムには制約が少ないので、RTL設計の初期段階から論理合成を行えます。

したがって、早期に論理合成可能か否かを判定する事ができます。

また、予期しないラッチ生成を早期に発見できる機会にも恵まれます。

詳細はこちらへ。

本書は、RTL記述の原則、および、RTL記述から合成回路を予測する手法を解説した技術資料です。

記述したデザインがどのような回路構成に合成されるかが随所で解説されているので、設計分野の初心者に役立つ資料です。

練習問題も追加されたので技術の習得を確認できます。全ての問題に解答が準備されています。

SystemVerilogで設計する技術者におすすめします。

詳細は、こちらへ。

今日では、ハードウェア記述言語はハードウェア設計・検証に欠かせない手段となっています。

本書は、ハードウェア記述言語を用いて回路を表現するために必要な基礎知識と効果的表現技術を解説しています。

ハードウェア記述言語としてSystemVerilogを採用しているので、解説は具体的、教育的、実用的であり、かつ実践的です。

本書を通して読者はハードウェア記述言語の役割・機能・効果を習得できます。

解説は、ハンティントンの公準によるブール代数の定義から始まり重要なブール代数の定理に完全な証明を与えています。

そして、公理を基にした理論で解説を進めているので、論理合成および論理の最適化は厳密かつ簡潔になっています。

特に、机上での論理合成と最適化手法を詳細に解説しています。

その他、本書では従来の思考法では思いにもよらなかった斬新な記述法によるRTL記述法も紹介しています。

また、FSMの章では、FSMの厳密な定義、具体例、SystemVerilogによるFSMの実装法を詳しく解説しています。

本書は、ハードウェア記述言語と論理回路の関りを理解するための最適な書物です。

ネット予約開始までもうしばらくお待ちください。

サンプルは、 こちらへ。

SystemVerilogの言語仕様は成熟期に到達し、SystemVerilogの機能を効果的に活用する時代に至りました。

旧態依然としたハードウェア記述法は時代遅れになり、現代的な発想と技術が求められています。

本書は、Verilog時代に行われていた時代遅れの発想と設計手法から脱皮し、現代的な発想を導く技術資料です。

誰もが知っているSystemVerilog機能でも、まだ殆どの人が気が付いていない効果的活用法が多くあります。

本書は、そのような技術を代表的例を通して紹介します。本書により、現代的な発想法を身に付ける事ができます。

資料サンプルはこちらへ。

共立出版より、「SystemVerilogによるモデリングと論理合成」が2026年1月23日に発売予定です。

現在、ネット予約受付中です。詳細は、 こちら へ。

共立出版社より発売される『SystemVerilogによるモデリングと論理合成』は以下の特徴を備えています。

★ 論理合成の原理とSystemVerilogによる現代的なモデリング手法を学べる面白い本です。

★ RTL記述から合成される回路構成を予測する知識・技術を習得できます。

★ ブール代数の基礎知識だけで論理の最適化手法を学べます。

★ 的確なRTLモデリング知識・技術を身に付けられます。

★ 従来の手法では思いにもよらなかった効果的なモデリング手法が解説されています。

★ Grayコードの特徴が詳しく解説されています。

★ ブール代数の解説及びFSMの厳密な定義もあるので技術者のみならず学生諸氏にもお勧めします。

SystemVerilogがIEEE標準規格となってから20年経過した現在、言語仕様に眠っている機能や新たな活用法を

模索する時期であると思います。

本資料は、完全な初心者を対象にしたSystemVerilogの入門書です。

解説は簡単なデザイン例から始まるので、学習初期にSystemVerilogの全体像を把握できます。

デザイン例から、読者は組み合わせ回路およびシーケンシャル回路の基礎知識を学べます。

基礎を理解できれば、後は言語的な知識の理解の積み重ねにより実践的な知識を習得できます。

予備知識なしでSystemVerilogを習得する最適な資料です。

詳細は、こちらへ。