製品

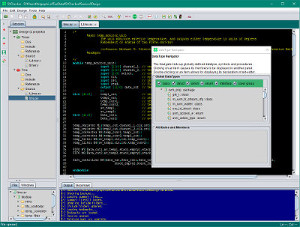

SystemVerilog IDE

SystemVerilog ライブラリー (SVL)

SystemVerilog クラスライブラリー (SCL)

|

ソフトウェアパッケージ

|

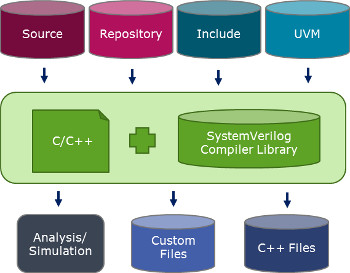

SystemVerilogの使用法が多様化するに伴いEDAツールベンダーからのサポートを期待できない機能分野が発生してきます。また、独自のユニークな設計・検証機能を開発しなければならない企業様も増えてきます。そのような状況においては、SystemVerilogコンパイラーを含むユーティリティの存在が不可欠になります。 |

サービス

受託業務

★ EDA全般のソフトウェア設計・開発業務をお受け致しています。

★ SystemVerilog 及び UVMに関する各種のご依頼を承ります。

お気軽にお問い合わせ下さい。