UVM支援機能

Verilog HDLからSystemVerilogへ移行し、多くのキーワード、シンタックス、文、命令等が追加されました。素朴なシンタックスを持つVerilog HDLと異なり、SystemVerilogの持つ機能を駆使する為には時代に即したツールの使用が不可欠です。ましてや、UVMは更に複雑な構造・機能を持つ為、設計・検証技術者に課される作業負担は想像を絶します。

単にシミュレータを実行するだけであれば、素朴なテキスト・エディタとコンソール・ターミナルがあれば任務を十分遂行する事が出来ます。然し、SystemVerilog 、及び、UVMを使用して検証環境を構築するとなると事情は全く異なります。素朴なテキスト・エディタだけでは生産性は向上しません。特に、UVMには必須の記述が多い事とそれぞれのキーワードが長い事が、利用者に不満を齎す主原因となっています。また、タイプミスは日常茶飯事で生産性向上の妨げになっているのが現状です。

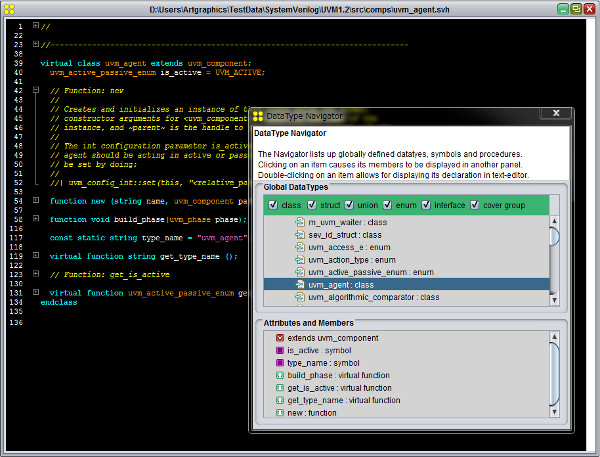

下図はUVMを支援する機能の一例を示しています。この例では、

行の折り畳み

クロス・リファレンスとしてのナビゲータ

FPS(File Positioning System)

等の役割を強調しています。行の折り畳みにより、uvm_agentクラスの仕様の閲覧が容易になっています。ナビゲータは、uvm_agentクラスのファイルを開く機能を提供しています。テキスト・エディタ右端の白い領域はFPSで、ファイルの任意の行に移動する制御をします。大きなファイルを開いている場合、スクロール・バーを上下する必要が無い為、生産性が向上します。たとえ些細な便利さでも技術者のフラストレーション緩和に大きな効果を齎します。

UVMを支援するテキスト・エディタとナビゲータ

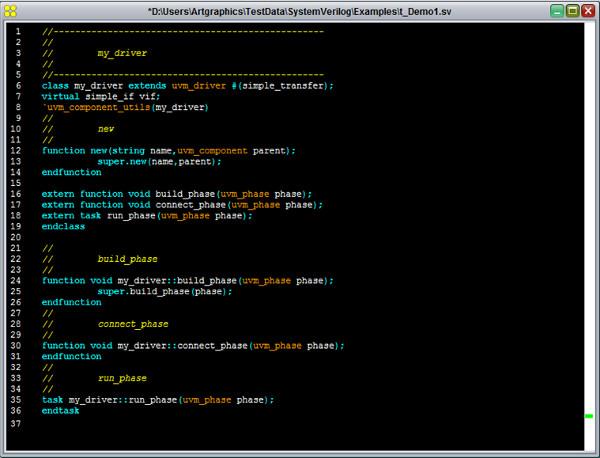

UVMには守るべきルールが沢山ありますが、忘れやすい事は確かです。検証コードを最初に準備する際は、どの様な場合でも殆ど同じです。従って、ウィザードが便宜を図れる恰好の機会です。以下に示す例は、ドライバーのテンプレートをUVMクラス・ウィザードで生成した例です。使用するphaseを選択するだけでコード・テンプレートを作成する事が出来ます。phaseメソッドをクラス内外に生成する制御も備わっています。

UVMクラス・ウィザードによるドライバー生成例

テキスト・エディタの詳細は、 こちら を参照して下さい。